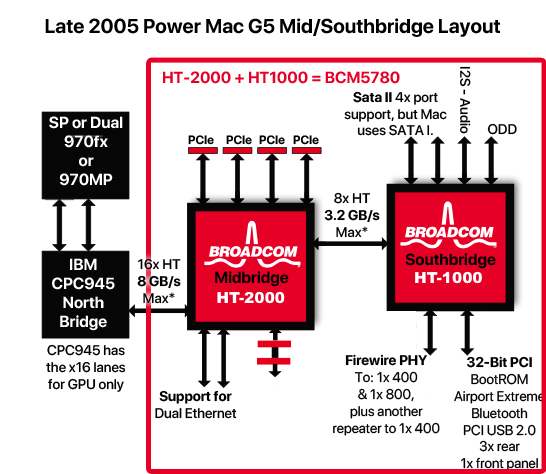

When the Dual-Core PowerPC 970MP third-generation G5 CPUs came out in Mid-2005, Apple had to start using a brand new Mid Bridge chip for the Macs along with it. Since the AMD 8131 only had PCI-X bridges and no PCIe bus, they couldn’t keep the old chip, replacing it with the BCM5780.

(Above: Block diagram for the BCM5780, aka HT2000 + HT1000 combined.)

(Above: Block diagram for the BCM5780, aka HT2000 + HT1000 combined.)

- See: Broadcom-HT-2000-PB03-R-2.pdf.zip (Download, 136 KB)

Broadcom says the HT-1000 can technically be used as a north or south bridge. In the BCM5780 configuration, HT2000 is the mid bridge, HT1000 is the south bridge.

Tech Specs

- Dual Broadcom BCM5714 Gigabit Ethernet (GbE) controllers

- VLAN tag support (IEEE 802.1q), L2 priority encoding (IEEE 802.1p), and Link aggregation (IEEE 802.3ad) and Universal Management Port (UMP) features, SMBus 2.0

.

- VLAN tag support (IEEE 802.1q), L2 priority encoding (IEEE 802.1p), and Link aggregation (IEEE 802.3ad) and Universal Management Port (UMP) features, SMBus 2.0

- 2-GHz (1-GHz, 2X) HyperTransport bus interface

- Up to 16x for side A to CPC945 Northbridge (Up to 8 GB/s aggregate*)

- * Aggregate total bandwidth. 16x HT transfer rates: up to 2000 Mb/s per wire

- Up to 8x for side B to Southbridge, etc; (Up to 3.2 GB/s aggregate*)

- Aggregate total bandwidth. 8x HT transfer rates: up to 1600 Mb/s per wire

.

- Aggregate total bandwidth. 8x HT transfer rates: up to 1600 Mb/s per wire

- Up to 16x for side A to CPC945 Northbridge (Up to 8 GB/s aggregate*)

- PCIe v1.0 and v1.0a compliant: Up to 17 total PCIe lanes. On a Power Mac G5 Late 2005, you could use up all the expansion slots including the GPU, and still have 1x PCIe lane leftover in the system! Up to 4 controllers.

- Slot 2: 4-Lane

- Slot 3: 8-Lane

- Slot 4: 4-Lane

- For a total of 16/17 lanes used, nothing including the 16 handled by the CPC945 for GPU.

.

- Compatible with 32 and 64-Bit CPUs, up to a Quad-Processor config. (Up to 8 CPUs/cores)

. - HT-2000 supports PCI-X 1.0 with up to 5 bus masters, replacing the older AMD 8131. Integrated PCI-X bus arbitration.

. - HyperTransport I/O link specification, Revision 1.05 compliant

. - Designed for 24/7 enterprise computing uptime, with Advanced error detection and correction

. - Chip info: SWC-HT2000-S07: PBGA 867LD Leaded

- SWC-HT2000-S07LF: PBGA 867LD Lead-Free

.

- SWC-HT2000-S07LF: PBGA 867LD Lead-Free

- Integrates all main server I/O interconnects: PCIe, PCI-X, and GbE