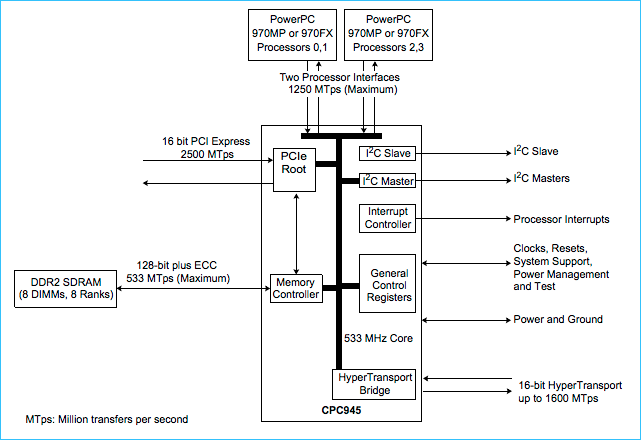

The IBM CPC945 is a redesigned Northbridge chip mostly for the Dual-Core PowerPC 970MP CPU. It has technical upgrades over the IBM CPC925, including a faster HyperTransport Bus. It’s also capable of talking to the PowerPC 970fx second-generation G5 chip, which means it may be found in other Late 2005 Macs on the logic board.

Released alongside the PowerPC 970MP and Xbox 360 XCPUs in Mid-2005, Apple calls it the U4 chip.

Fun fact: On Power Mac G5s, the South Bridge controller chip, which is different from the Northbridge, contains a 33 MHz PCI bus, for some Mac functions: The Boot ROM, Bluetooth, Airport Extreme, and a PCI USB 2.0 controller. This 33 MHz PCI bus is largely unchanged from the original through the last G5.

- See: IBM_CPC945_Northbridge_Datasheet.pdf.zip (Download, 1.1 MB)

.

Key points about the CPC945

- Capable of supporting two chips, like the CPC925 (prior one)

. - Has two, 625 MHz Unidirectional CPUinterfaces (typical), but the processor interface bus in a Late 2005 Power Mac G5 runs at half the processor speed instead.

. - Processor Interfaces are 625 MHz DDR2, 1250 MTps Max

. - Two memory controllers: Which support up to 64 GB of 533 MHz DDR2 SDRAM with ECC.

. - Up to 16x Hypertransport for side A to Mid (Up to 8 GB/s aggregate*)

- Up to 8x Hypertransport for side B (Up to 3.2 GB/s aggregate*)

- *In a prior publication of this article, information was incorrectly listed where the 16x interface would do up to 12.8 GB/s. This was a mathematical calculation off of inaccurate data, and has since been fixed. “GB/s” informational references have been updated here to reflect this. There may be more minor corrections on this specific publication within the next day or two to reflect full informational accuracy.

. - 1.5 Volt, 533 Mhz core

. - 128-Bit, Error Correcting Code (ECC) 533 MTps 1.8 Volt DDR2 RAM Bus = 4.264 GB/s

. - The CPC945 only handles one x16 PCIe slot, for graphics. Only Slot 1 connects directly to the Northbridge chip. The remaining PCIe devices in a Power Mac G5 Late 2005 connect to the Mid-Bridge PCI-Express and HyperTransport tunnel.

. - 1182-pin flip-chip plastic ball grid array (FC-PBGA)

. - Support for up to 8x paired 64/72-bit Double-Sided Dual Inline Memory Modules (DIMMs)

. - Power management support for the CPC945 through clock control

. - DMA address relocation table (DART), and a system interrupt controller (MPIC)

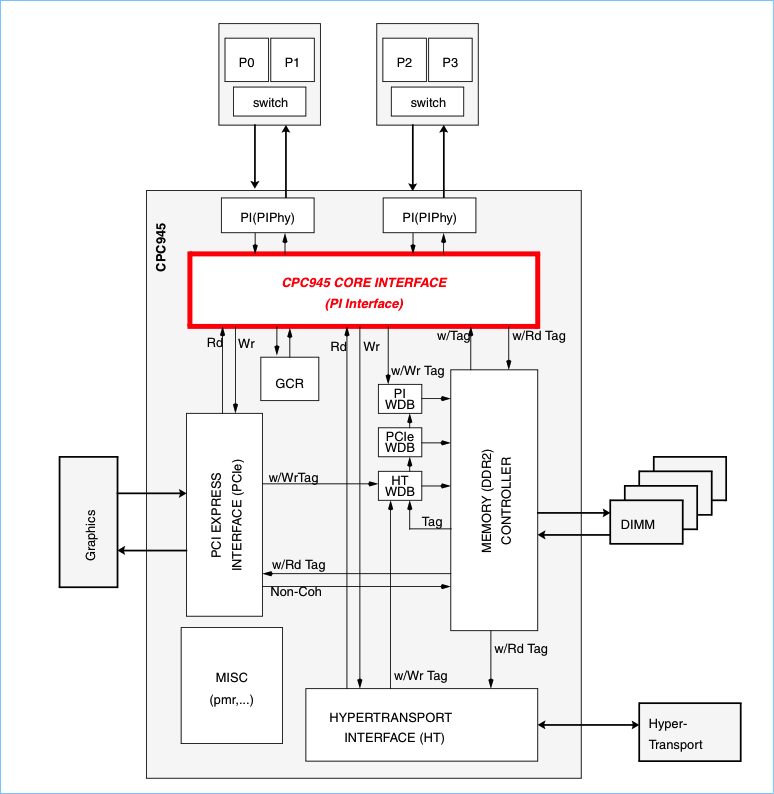

In the Mac OS X System Profiler, the CPC945 appears as a CPU interface to the PCIe root complex and HT host bridge, a memory and interrupt controller, as well as a set of control registers. It’s basically “part two” of any G5 chip, bringing much of the rest of the Mac’s core functionality together.

.

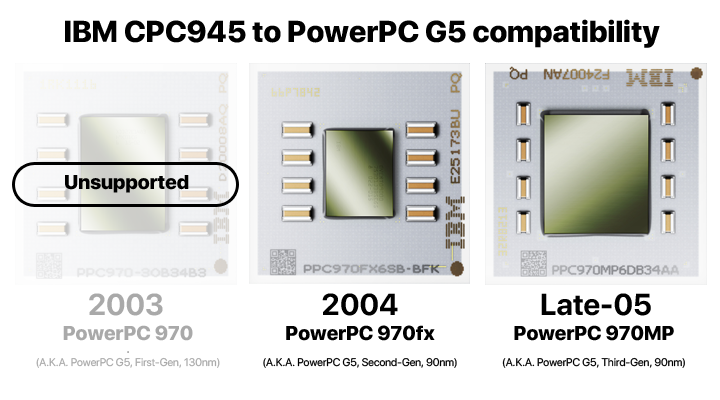

Processor Interfaces and compatibility

Although it’s not known whether or not a CPC945 has ever been paired with a first-generation 970, it is easier to say it’s unsupported. By the time this chipset and those chips came out, IBM already moved onto 90 nanometers, away from the 130 nanometer fabrication size of the 970 and CPC925. Theoretically it may be equally as possible as it may be not, to pair the older chip with the newer chipset.

.

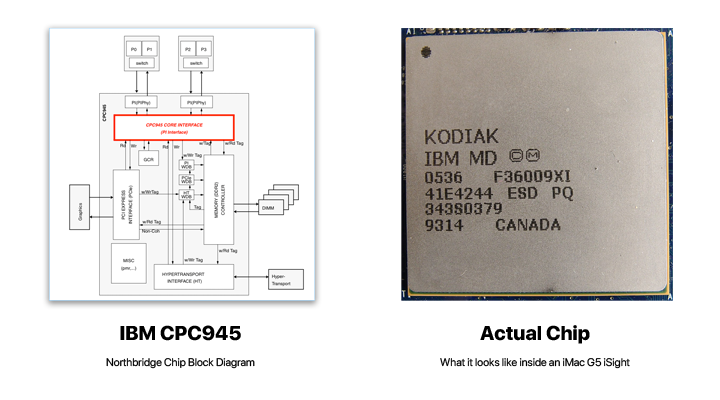

Northbridge Block Diagram

.

.

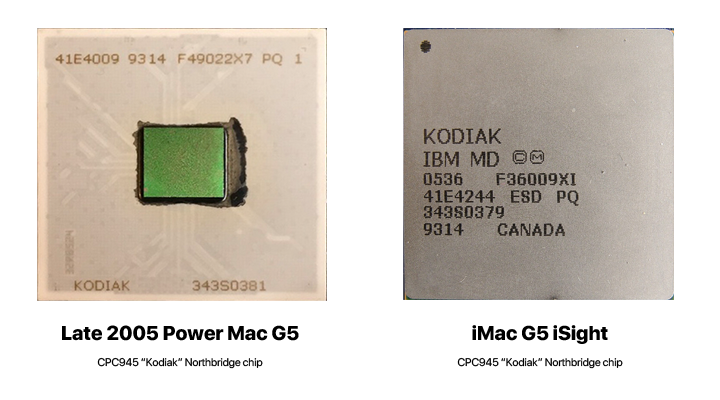

Visual differences between the different Macs